Dye-and-Pry-Experimente mit Simulationen reduzieren

Systeme mit hoher Rechenleistung nutzen oft Bausteine im Ball Grid Array (BGA). Bereits in der Entwicklungsphase erfordern BGAs eine robuste Konstruktion und Optimierung, damit sie zuverlässig mit der Leiterplatte kontaktieren. Dabei lassen sich die Lötergebnisse durch Simulationen verbessern.

Simulationen statt Dye-and-Pry-Experimente

Ball Grid Arrays (BGA) sind integrierte Schaltkreise mit sehr vielen Anschlüssen. Diese zuverlässig auf eine Leiterplatte zu löten, ist eine große Herausforderung. Verantwortlich dafür ist der unterschiedliche Wärmeausdehnungskoeffizient (Coefficient of Thermal Expansion, CTE) zwischen Bauteil, Lot, Kupferpad und Leiterplatte. Dadurch verformen sich die Materialien, wenn sie während dem Lötvorgang erst erhitzt und anschließend abgekühlt werden. So können Risse entlang der intermetallischen Phase der Lötverbindung entstehen. Wie zuverlässig eine Lötstelle ist, bestimmt sich vor allem dadurch, wie stark ein Produkt thermisch belastet wird, und wie die Metallurgie der Verbindung aussieht. Neben diesen Umweltfaktoren beeinflusst auch das Kriechverhalten der Lotlegierung die Zuverlässigkeit.

Üblicherweise nutzen Board-Hersteller sogenannte Dye-and-Pry-Experimente, um die Fertigungsparameter zu optimieren. Für Dye-and-Pry wird zunächst eine ganze Serie an Boards mit verschiedenen Prozessparametern gefertigt. Anschließend kommen die bestückten Platinen in ein Bad mit einer hochviskosen, farbigen Flüssigkeit (engl. Dye). Aufgrund der Kapillarwirkung dringt diese Flüssigkeit bis in die mikroskopisch feinen Risse ein, die sich durch den Temperaturstress zum Beispiel bei den Lötkugeln (Balls) des BGAs gebildet haben. Danach werden die Komponenten mechanisch von den Platinen heruntergerissen (engl. Pry) und die Grenzflächen auf Risse untersucht, was die farbige Flüssigkeit in den Rissen natürlich sehr erleichtert.

Dieses zerstörende Verfahren ist eine regelrechte Materialschlacht und daher mit hohen Kosten verbunden. Interne Berechnungen von Zollner zeigen, dass der experimentelle Aufwand etwa 45 Mal höhere Kosten als eine Simulation verursacht. Ziel der nachfolgenden Untersuchung war es also, ob sich die Fertigungsparameter zerstörungsfrei auch per Simulation optimieren lassen.

Reale Welt und Simulation stimmen überein

Nachdem ein Ersatzmodell in Ansys Workbench erstellt ist, werden die thermischen Randbedingungen in Form eines Reflow-Lötprofils (hier Sattelprofil) aufgebracht. Die viskosen und plastischen Effekte des Lotes lassen sich durch das Anand-Modell [1] abbilden, um das Kriechen als primären Schadensmechanismus von Lötstellen zu modellieren. Das Tool Ansys Sherlock bietet hier bereits umfassende Einblicke auf Leiterplattenebene. Dabei erleichtern im ersten Schritt Lebensdauerabschätzungen die Identifizierung von kritischen Bauteilen.

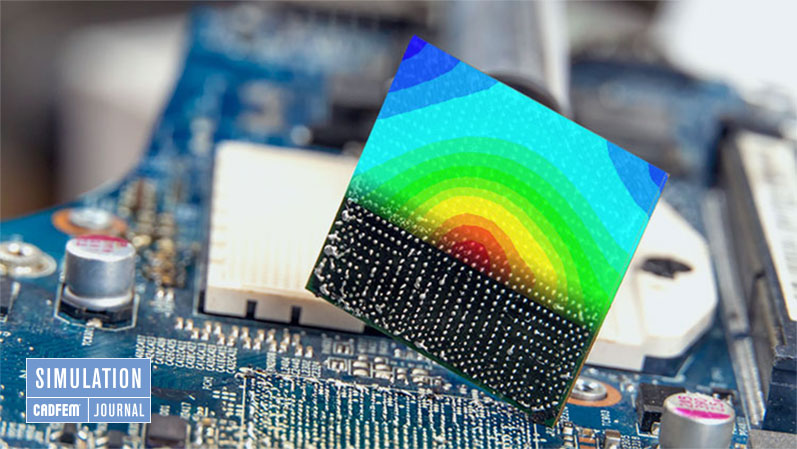

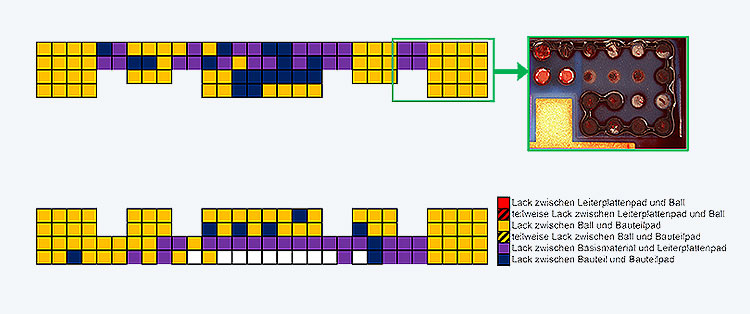

Als Ergebnis der Simulation und für die Quantifizierung des Schadens dient die Dichte der Kriechdehnungsenergie (Creep Strain Energy Density – CSED). Diese lässt sich mit einem angepassten APDL-Skript (Ansys Parametric Design Language) bestimmen. Im folgenden Bild sind die experimentellen Ergebnisse aus den Dye-and-Pry-Versuchen und die CSED aus der Simulation gegenübergestellt. Gut zu erkennen ist, dass reale und numerische Welt weitestgehend übereinstimmen und kritische Verbindungen sowie die Durchbiegung von Bauteil und Leiterplatte sichtbar werden. Außerdem wurde die Lebensdauer der gesamten bestückten Platine prognostiziert, um weitere kritische Komponenten zu identifizieren.

Prädiktive Analyse auf Ebene der Lötkugeln

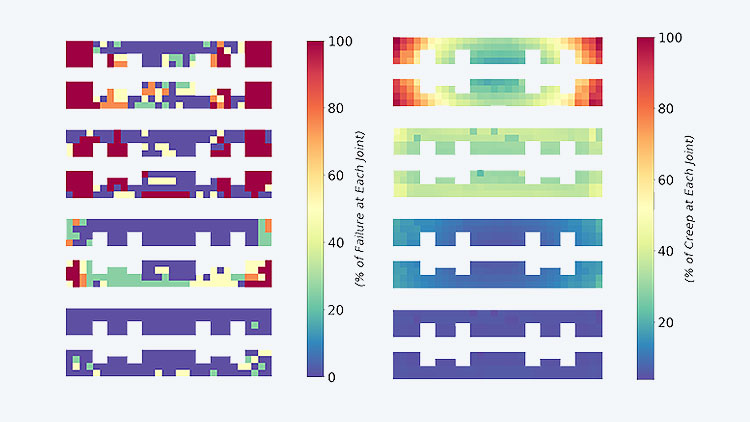

Mit der logistischen Regression kombiniert man die experimentellen Ergebnisse mit den berechneten CSED-Werten (als unabhängige Variable) aus Ansys Workbench zu einer prädiktiven Analyse auf Ebene der Lötkugeln. Um zu überprüfen, wie gut diese Anpassung ist, kam zunächst ein Likelihood-Ratio-Test zum Einsatz. Mit diesem Hypothesentest lässt sich die Güte der Anpassung von zwei Modellen (einem uneingeschränkten Modell, dessen Parameter alle frei sind, und dem entsprechenden, von der Nullhypothese auf wenige Parameter eingeschränkten Modell) an die Stichprobendaten vergleichen. Der Korrelationskoeffizient Pseudo-R² nach McFadden ist ein Maß für die Varianz jedes Prädiktors (die zur Vorhersage eines Merkmals herangezogene Variable) für die abhängige Variable. Dies dient als weiteres Qualitätsmaß für das Modell. Mit dem Wald-Test lassen sich die Prädiktoren statistisch daraufhin überprüfen, wie wichtig diese jeweils für die Modellgüte sind.

Abschließend werden die statistischen Modelle anhand der ROC-Kurve (Receiver Operating Characteristic) analysiert. Die Fläche unter dieser Kurve (Area under Curve – AUC) bestimmt, welches Modell zur prädiktiven Analyse letztlich verwendet wird.

Simulation für ein fertigungsgerechtes Design

Bei der Produktion von Leiterplatten spielen viele Einflussfaktoren (z. B. Verwindung/Verwölbung, Materialmix, Lotlegierung etc.) eine große Rolle. Die experimentellen Ergebnisse des Dye-and-Pry-Tests und die berechnete Dichte der Kriechdehnungsenergie (CSED) aus Ansys stimmen weitestgehend überein. Dies macht die Entwicklung eines prädiktiven Modells für Ausfallwahrscheinlichkeiten während des Lötprozesses möglich. Simulation kann hier also kostenintensive Experimente zu weiten Teilen ersetzen.

Wie die gefundenen Ergebnisse in die Praxis umgesetzt werden sollen, ist noch in der Evaluierung. Denkbar sind beispielsweise neue Regeln für das fertigungsgerechte Design von Leiterplatten – Stichwort »Design for Manufacture«.

Komplexe mechatronische Systeme, von der Entwicklung bis zum After Sales Service: Als Partner global agierender Spitzenunternehmen sowie kleiner und mittelständischer Betriebe bietet die Zollner Elektronik AG branchenübergreifende Systemlösungen entlang des gesamten Produktlebenszyklus.

Das Unternehmen wurde 1965 in Zandt, Bayern gegründet und ist heute eine Aktiengesellschaft, die sich zu 100 % in Familienbesitz befindet. Durch kontinuierliches organisches Wachstum hat sich die Zollner-Unternehmensgruppe als Mechatronik-Dienstleister unter den Top 15 der EMS-Dienstleister weltweit etabliert.

Individuelle, persönliche Betreuung ist uns wichtig – sie beginnt bei der gesamtheitlichen Beratung und setzt sich über alle Phasen der Zusammenarbeit fort.

An 20 Standorten in Deutschland, Ungarn, Rumänien, China, Tunesien, den USA, der Schweiz, Costa Rica und Hongkong setzen wir auf Qualität, optimales Preis-Leistungs- Verhältnis, technologischen Vorsprung und eine Best-Cost-Country-Strategie entlang der gesamten Wertschöpfungskette. Egal, ob es sich um Einzelteile, Module, Geräte oder komplexe Systeme handelt: Der Kunde entscheidet über die Prozesstiefe.

Zollner Elektronik AG

Manfred-Zollner-Str. 1

93499 Zandt

www.zollner.de

Autoren:

Philemon Olaleru (Zollner Elektronik AG),

Dr. Tim Weber (Zollner Elektronik AG),

Prof. Dr. Peter Firsching (Technische Hochschule Deggendorf)

Referenzen:

[1] Anand, L. (1985). Constitutive equations for hot-working of metals. International Journal of Plasticity, 1(3), 213–231. doi.org/10.1016/0749-6419(85)90004-X

Erstmalig veröffentlicht in Design&Elektronik, 02/2021

www.design-elektronik.de